一、静电容易损坏MOS的根本原因

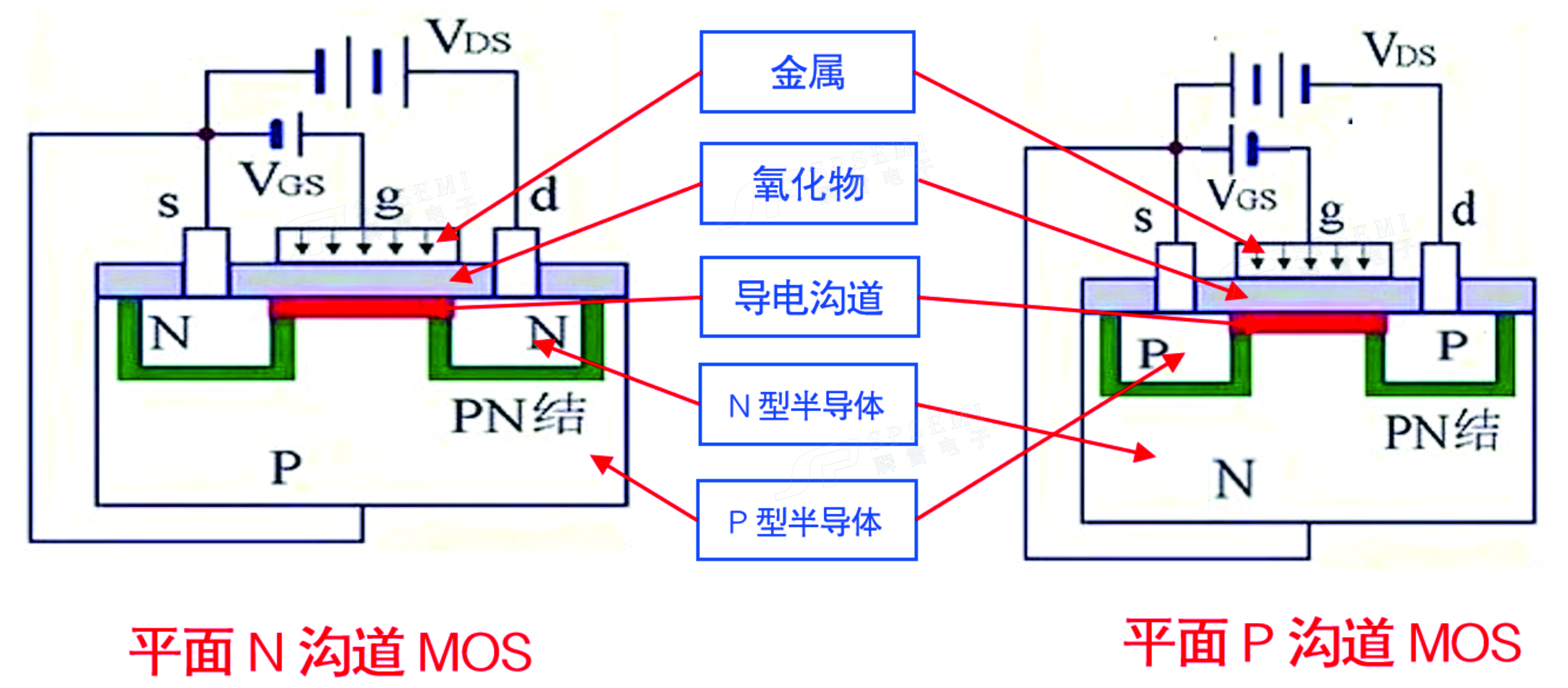

1、以平面MOS结构为例,如图所示:

2、MOS工作原理:在N沟道MOS中,源极S与P型半导体相连,VDS为反向二极管不导通,VSD为正向二极管(N沟道MOS内的体二极管)可以导通。所以漏极D到源极S间导通需要在栅极g上施加正向电压,由栅极与半导体间由绝缘层隔离,电荷在栅极上产正电场,按电场规律同性相斥异性相吸的原理,对多子为电子(带负电)的N型半导体中的电子产生吸引力,反之多子为空穴(正电)的P形半导体中的空穴产生排拆力,大量电子在绝缘层下堆积形成导电沟道,连通源极S、漏极D的N形半导体形成导通沟道,漏源极导通。P沟道加反向电压形成负电场,原理相同,极性相反。

3、如图中红色区域的导电沟道,其导电能力取决于沟道的导通电阻:

沟道电阻R(内阻)=ρ(电阻率)×L(沟道长度)/S(沟道面积)

其中ρ电阻率取决于N型半导体中多子(电子)的数量,即N型半导体掺杂浓度 。

其中L取决于沟道的长度,即芯片版图设计尺寸或MOS击穿电压的大小相关。

其中S导电沟道的面积取决于沟道的大小,与N型半导体的掺杂浓度和栅极电场强决定。

按以上公式可以看出,S越大(沟道越宽),沟道导通电阻越小,导电能力越强。

4、通过以上公式可以看出,决定MOS导电能力的三个主要的因素中,由于MOS成型后电阻率ρ、沟道长度L已无法改变,唯一可变因素只有S,即通过栅极电场的大小改变导电沟道的宽度,进一步改变MOS漏源电流的大小。

5、但是栅极电场越高,为避免绝缘层损坏,氧化物的绝缘层必然越厚,绝缘层越厚,MOS最小开启电压VGS(th)必然越高,同时因结电容变大原因开启时间也越长,就失去了MOS低开启低功耗高频率的优势;为了解决这样的矛盾,目前市面上大多MOS产品的VGS上限规定在±20V以内,即栅极电场施加的电压不能高于20V,否则MOS作为开关器件或大规模集成电路器件的优势将荡然无存。

6、MOS栅极电压低,加上其结构特点,注定无法抵抗高电压的冲击,这就是MOS栅极容易损坏的主要原因。